電話:15301560529

新聞

News

等離子體刻蝕面臨的挑戰

點擊量:645 日期:2023-08-21 編輯:硅時代

近幾十年來,等離子刻蝕技術已取得了長足發展。利用等離子刻蝕技術,人們得以準確地雕刻器件結構,從而為晶體管尺寸的縮小以及性能的提升提供了保障。但是,當前的先進芯片關鍵尺寸更小,有些還具有三維結構(如FinFETs和3D NAND),這無疑對當前的等離子刻蝕技術提出了挑戰。

均勻性一直是刻蝕工藝的一大考量。關鍵器件結構尺寸的允許工藝誤差一般約為其自身尺寸的10%。例如,寬度為 10nm 的晶體管柵極結構,其允許誤差僅為 1nm,相當于3至4個原子層。

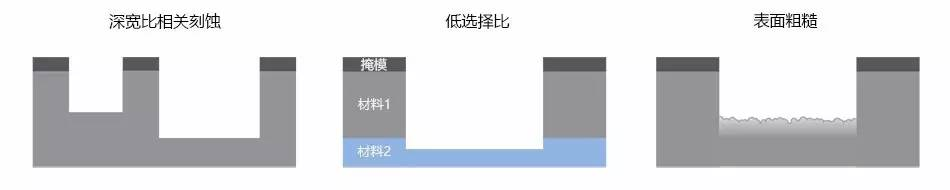

隨著結構尺寸的不斷縮小,人們需要盡可能地降低由各種原因導致的工藝誤差。不同尺寸的結構在刻蝕中的速率差異是誤差產生的重要原因之一。這種深寬比相關刻蝕(ARDE)會導致高深寬比結構的刻蝕速率要比低深寬比結構的刻蝕速率低。

另一項挑戰則在于,刻蝕工藝需要在去除目標材料的同時,完好地保留下一層材料。

例如,一個薄膜堆棧由多層材料組成,我們可能只要去除最上面的那層(材料 1),而同時不能去除或損壞下層(材料 2)。材料 1 和材料 2 的刻蝕速率比稱為“選擇比”,很多刻蝕工藝都要求具有極高的選擇比。

第三項挑戰在于,當達到期望的深度之后,等離子體中的高能離子可能會導致硅片表面粗糙或底層損傷,這是需要極力避免的問題。對于最先進的芯片,工程師們需要對上述參數進行更嚴格的控制,以期獲得原子級高保真度。